LVDS-компоненты National Semiconductor для MULTI-DROP-применений

![]()

Cистема передачи низковольтных дифференциальных сигналов LVDS появилась в 1994 году и была обусловлена потребностями в повышении скорости передачи данных по витой медной паре в компьютерном и коммуникационном оборудовании. Поскольку LVDS является дифференциальной системой, она основана на принципе разности амплитуд напряжения, которые в дальнейшем идентифицируются и сравниваются приемником. Таким образом, передаваемая информация кодируется разностью напряжений на двух проводниках линии связи. Собственная емкость линии связи определяется величиной согласующих резисторов (80...120 Ом), которые подключаются к обоим концам линии связи, а также значением используемой для кодирования информации разности амплитуд напряжений. Например, если драйвер (передатчик) питает линию током 3,5 мА, то на согласующем резисторе будет выделяться мощность примерно 1,2 мВт. Если сравнить это значение с рассеиваемой мощностью 90 мВт, выделяемой на согласующем резисторе линии RS-422, то становится очевидным преимущество LVDS-системы - большая экономичность

LVDS-сигналы в настоящее время широко применяются в высокоскоростных компьютерных шинах. В качестве примеров можно привести FireWire, SCSI, Serial ATA, RapidIO и многие др. Требования к LVDS-системам и сигналам описываются двумя промышленным стандартами. Более распространенным из них является стандарт ANSI/TIA/EIA-644, разработанный ассоциацией телекоммуникационной промышленности США (ассоциация TIA), который описывает общие требования к электрическим характеристикам сигналов. Другой стандарт, разработанный институтом инженеров по электротехнике и электронике (IEEE), описывает специфические требования к LVDS-системе, которая применяется в составе масштабируемого когерентного интерфейса (SCI). Стандарт ANSI/TIA/EIA-644 определяет требования к электрическим характеристикам драйвера и приемника. Требования к протоколу связи не входят в стандарт TIA. Стандарт IEEE 1596.3 SCI-LVDS изначально был ориентирован на дифференциальный PCL-интерфейс, поэтому, SCI-LVDS следует понимать как разновидность интерфейса SCI. Стандарт описывает требования, как к электрическим характеристикам, так и к протоколу кодирования и декодирования передаваемой информации.

Общие сведения о топологиях LVDS-систем

LVDS-система реализуется по одной из трех топологий, представленных на рисунке 1, или их комбинаций. Топология POINT-TO-POINT применяется для построения последовательных или параллельных быстродействующих шин передачи данных. В зависимости от конкретного применения, топология POINT-TO-POINT может быть симплексной (рис. 1а), полудуплексной (рис. 1б) или полнодуплексной (рис. 1в).

Рис. 1. Топологии LVDS-систем

Топология MULTI-DROP используется в системах, в которых несколько LVDS-компонентов необходимо синхронизировать общим LVDS-сигналом синхронизации. Такое решение позволяет добиться максимальной надежности функционирования системы синхронизации. Топология MULTI-DROP также используется в тех случаях, когда одно ведущее устройство передает одну и ту же информацию нескольким подчиненным устройствам, подключенным к общей шине. Топология MULTI-POINT LVDS (или M-LVDS) появилась недавно, ее появление было вызвано потребностями построения систем, в которых несколько LVDS-трансиверов подключаются к общей линии связи. К компонентам такого трансивера (драйвер и приемник) предъявляются несколько иные требования, изложенные в отдельном стандарте TIA/EIA-899. В частности, изменения коснулись пороговых уровней приемника. Стандартом TIA/EIA-899 определяется два типа приемников с различными пороговыми уровнями (см. рис. 2). Кроме того, этим стандартом предписываются особые требования по управлению фронтами сигналов.

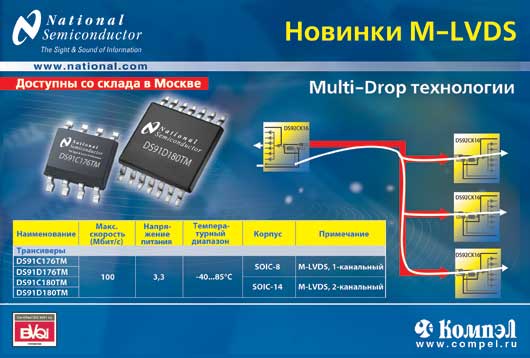

Компоненты National Semiconductor для MULTI-DROP-применений

Ранее уже упоминалось, что основным применением топологии MULTI-DROP является построение системы распределенной синхронизации, которая бы обеспечивала высокое быстродействие и малые дрожания. Компания National Semiconductor предлагает широкий выбор продукции для реализации топологии MULTI-DROP, в т.ч. драйверы и приемники с одним (1:1) или несколькими выходами (1:n). Сориентироваться в выборе этой продукции помогут таблица 1 и рисунок 3.

Таблица 1. Краткая характеристика компонентов National Semiconductor для MULTI-DROP-применений| Наименование | Кол-во драй- веров | Кол-во прием- ников | Совмести- мость входа | Выход | Макси- мальное быстро- действие канала, МГц | Корпус | Примечания |

|---|---|---|---|---|---|---|---|

| Драйверы | |||||||

| DS91C176TM/ D176TM | 1 | 1 | M-LVDS/ LVDS | M-LVDS | 100 | SOIC-8 | Полудуплекс, управляемая скорость фронтов |

| DS91C180TM/ D180TM | 1 | 1 | M-LVDS/ LVDS | M-LVDS | 100 | SOIC-8 | Полный дуплекс, управляемая скорость фронтов |

| DS92LV010ATM | 1 | 1 | LVDS/ LVPECL/ CML | B-LVDS | 80 | SOIC-8 | Работа при 3,3 или 5 В |

| DS92001TM/ TLD | 1 | 1 | LVDS/ LVPECL/ CML | B-LVDS | 200 | SOIC/ LLP-8 | Управляемая скорость фронтов, флаг LOS |

| DS92LV040ATLQA | 4 | 4 | LVDS/ LVPECL/ CML | B-LVDS | 100 | LLP-44 | Управляемая скорость фронтов, малый перекос |

| Приемники (1:1) | |||||||

| DS91C176TM/ D176TM | 1 | 1 | M-LVDS/ LVDS | M-LVDS | 100 | SOIC-8 | Полудуплекс, тип 2/1, широкий диапазон синфазных напряжений |

| DS91C180TM/ D180TM | 1 | 1 | M-LVDS/ LVDS | M-LVDS | 100 | SOIC-14 | Полный дуплекс, тип 2/1, широкий диапазон синфазных напряжений |

| DS90LV012ATMF/ ATLD | 0 | 1 | LVDS/ LVPECL/ CML | LVTTL | 200 | SOT23-5, LLP-8 | Расположение выводов, облегчающее трассировку платы, миниатюрные корпуса |

| DS90LT012ATMF/ ATLD | 0 | 1 | LVDS/ LVPECL/ CML | LVTTL | 200 | SOT23-5, LLP-8 | Расположение выводов, облегчающее трассировку платы, миниатюрные корпуса |

| DS90LV028ATM | 0 | 2 | LVDS/ LVPECL/ CML | LVTTL | 200 | SOIC-8 | Расположение выводов, облегчающее трассировку платы |

| DS90LV048ATM/ ATMTC | 0 | 4 | LVDS/ LVPECL/ CML | LVTTL | 200 | SOIC/ TSSOP-16 | Расположение выводов, облегчающее трассировку платы |

| Приемники (1:n) | |||||||

| SCAN90CP02SP/ VY | 2 | 2 | LVDS/ LVPECL/ CML | LVDS | 750 | LLP-28/ LQFP-32 | Програм- мируемая коррекция предыска- жений, интерфейс JTAG, 1149.6 |

| DS90CP04TLD | 4 | 4 | LVDS/ LVPECL/ CML | LVDS | 1250 | LLP-32 | Очень малые дрожания, малое посадочное место |

| DS92CK16TMTC | 1 | 6 | LVDS/ LVTTL | VTTL и B-LVDS | 125 | TSSOP-24 | Поддержи- ваемые конфигура- ции: A) LVTTL-вход, до 6 LVTTL- + 1 BLVDS-выходов B) LVDS-вход, до 6 LVTTL-выходов |

| DS90LV110ATMT | 1 | 10 | LVDS/ LVPECL/ CML | LVDS | 200 | TSSOP-28 | Малые дрожания выходных сигналов |

| Прим.: Вся продукция рассчитана на работу в промышленном температурном диапазоне: -40...85°С. | |||||||

Рис. 3. Компоненты National Semiconductor для MULTI-DROP-применений

Рис. 4. Расположение выводов DS91C176/DS91D176 и DS91C180/DS91D180

ИС DS91C176TM/D176TM и DS91C180TM/D180TM (рис. 4) являются одной из последних разработок National Semiconductor и представляют собой быстродействующие M-LVDS дифференциальные трансиверы. Эта разработка может использоваться в MULTI-DROP-применениях (например, для распределения сигналов синхронизации на объединенных платах с шиной ATCA, являющейся улучшенной по быстродействию версией CompactPCI). DS91C176TM/D176TM и DS91C180TM/D180TM полностью отвечают требованиям нового интерфейсного стандарта M-LVDS (TIA/EIA-899), в т.ч. - по улучшенной нагрузочной способности (возможность подключения до 32 нагрузок) и управляемой скорости фронтов сигналов (позволяет минимизировать отражения сигналов и электромагнитные излучения). Их минимальная длительность фронтов, равная 1 нс, позволяет работать с ответвлениями длиной до 5 см. За счет расширенного диапазона синфазных напряжений улучшен запас устойчивости к действию шума. DS91C176/DS91D176 - полудуплексный трансивер в корпусе SOIC-8, драйвер которого преобразует входящие LVTTL/LVCMOS-сигналы в дифференциальный M-LVDS сигнал, а приемник преобразует низковольтные дифференциальные сигналы (LVDS, B-LVDS, M-LVDS, LV-PECL) в 3-вольтовые LVCMOS-сигналы. DS91C180TM/D180TM идентичен по электрическим характеристикам, а отличается тем, что поддерживает полнодуплексную конфигурацию и размещается в корпусе SOIC-14. Суффикс «D» означает, что встроенный приемник является 1-го типа, а «C» означает, что приемник относится ко 2-му типу. Приемники 2-го типа поддерживают возможность работы в отказоустойчивой конфигурации по типу монтажного «ИЛИ», что достигается смещением пороговых уровней на 100 мВ (см. рис. 2).

Журнал "Новости Электроники", номер 12, 2007 год.

Журнал "Новости Электроники", номер 12, 2007 год.