|

А. Строгонов Схемотехника элементов БИСПроцесс создания цифровой БИС состоит из двух взаимосвязанных этапов: логического и схемотехнического проектирования, включающего в себя совокупность задач выбора технологического базиса, преобразования логических схем в электрические схемы на транзисторном уровне, выбора схемотехнических решений базовых элементов, способов синхронизации, перехода от электрических схем к топологии кристалла. Эффективное схемотехническое решение базового элемента БИС может существенно улучшить технические характеристики и уменьшить площадь кристалла БИС. Наиболее сложные схемотехнические решения базовых элементов в современных БИС применяются только при их апробации. Наличие библиотеки схемотехнических решений базовых элементов БИС, описание их структуры, возможные их модификации, правила применения в составе БИС, аттестация с помощью программы SPICE являются необходимым условием успешного решения комплекса задач схемотехнического проектирования современных БИС. Схемотехника КМОП-вентилей БИС Модель n-канального транзистора представим в следующем виде (рис. 1а):

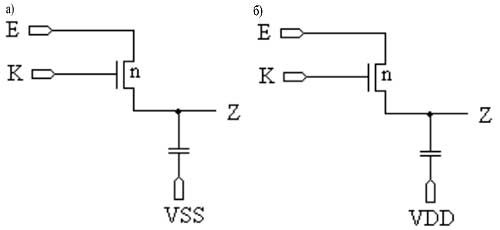

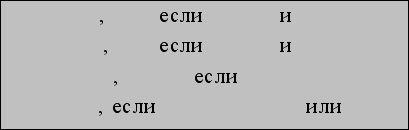

где t = 0,1,2,┘ - тактовое время, выбираемое исходя из быстродействия схемы, но гарантирующее устойчивое завершение в ней переходных процессов к концу такта; Et, Kt - входные информационный и управляющий сигналы, доопределяемые в алфавите A3 = {0,1,c} без уч╦та силы логического сигнала (входные слабые информационные сигналы полагаются неопредел╦нными (x), а входные слабые управляющие сигналы полагаются сильными (0, 1 или x)); Ztn - выходной информационный сигнал, значения которого обозначаются в квадратных скобках. На рис. 1б приведена схема p-канального МОП-транзистора. На рисунке VSS - шина Земля, VDD - шина Питание. Рисунок 1. Схемы n-канального (а) и p-канального (б) МОП-транзисторов с нагрузочными емкостями

В модели учтено, что при открытом канале отрицательный входной информационный сигнал переда╦тся без ослабления через n-канальный транзистор, тогда как положительный сигнал переда╦тся с ослаблением его силы. При закрытом канале на истоке имеет место динамическое хранение предшествующего состояния стока, которое считается слабым сигналом. В отличие от n-канального транзистора, p-канальный открывается отрицательным сигналом на затворе. Он ослабляет отрицательный входной информационный сигнал. Для построения КМОП-вентилей применяются три типа соединений транзисторов:

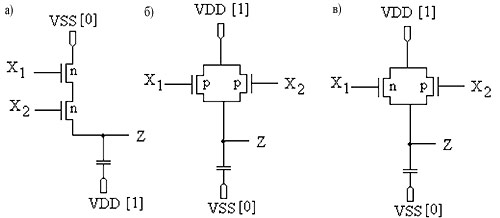

Рисунок 2. Виды соединений МОП-транзисторов, используемые для построения КМОП-вентилей:а) последовательное соединение однополярных n-транзисторов; б) параллельное соединение однополярных p-транзисторов; в) параллельное соединение комплементарных транзисторов

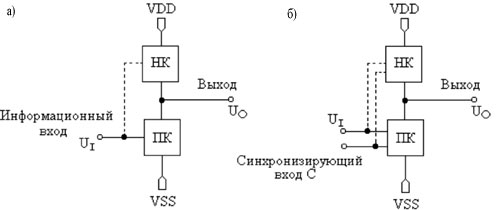

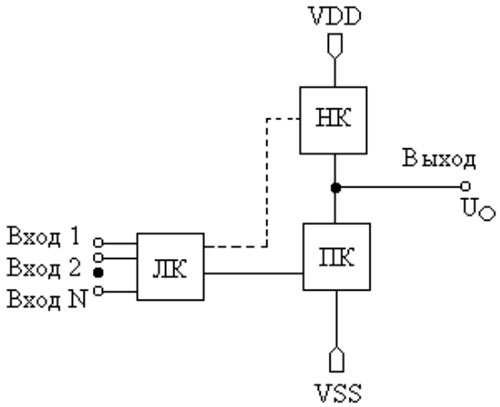

Простейшая структура базового логического элемента состоит из двух компонентов (рис. 3): переключательного ПК, выполняющего преобразования входной информации UI, и нагрузочного НК, позволяющего сформировать необходимые уровни выходных сигналов U0. Нагрузочный компонент может быть как управляемый входным сигналом UI, так и неуправляемым (штриховая линия на рис. 3). По способу передачи информации логические элементы можно разделить на две группы: асинхронные либо статические и синхронные либо динамические. Рисунок 3. Общая структура базового логического элемента: а) статического; б) динамического

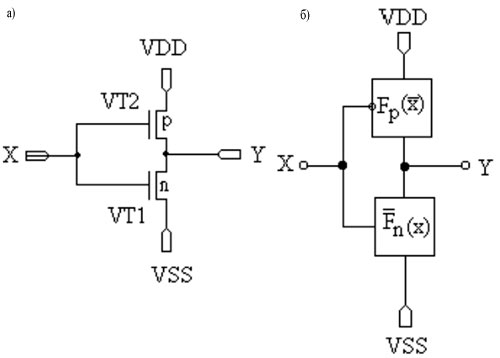

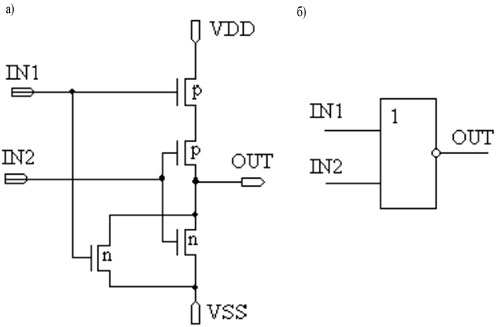

Структура логических элементов первой группы приведена на рис. 4. Время формирования выходного сигнала U0 определяется собственным временем задержки логического элемента. В динамических элементах время задержки формирования выходного сигнала квантуется в определ╦нные моменты времени, устанавливаемые частотой сигнала, подаваемого на синхронизирующий вход С (рис. 3б). Структурная организация статического КМОП-вентиля показана на рис. 4. Вентиль состоит из n- и p-канальных частей, которые реализуют дополнительные логические функции ¯Fn(x) и Fp(¯x). При этом в статическом режиме, когда входы схемы принимают произвольные значения из алфавита A2 = (0,1), одна часть схемы, соответствующая, например, функции ¯Fn(x), открыта, а другая, соответствующая Fp(¯x), закрыта. Поэтому в статическом режиме КМОП-схемы имеют чрезвычайно малый ток потребления. Структура логического элемента, показанная на рис. 4, имеет один информационный вход, вследствие чего он выполняет простейшие логические преобразования входного информационного сигнала. Поэтому для расширения функциональных возможностей в схему логического элемента вводят дополнительный многовыводной логический компонент (ЛК). ЛК может быть введ╦н либо на входе (рис. 5), либо на выходе и позволяет формировать логическую функцию от N входных информационных сигналов либо N выходных функций одного входного сигнала. Пример построения статического вентиля ИЛИ-НЕ и его условное графическое обозначение (УГО) представлены на рис. 6а,б. При построении вентиля учтено, что при корректном включении схемы в устойчивом состоянии на входы подаются сигналы 0 или 1, а выход OUT всегда коммутируется с одним из источников 0 шина VSS или 1 шина VDD. Рисунок 4. Электрическая (а) и структурные (б) схемы статического КМОП-вентиля

Рисунок 5. Многовходной базовый элемент

Рисунок 6. Пример реализации вентиля ИЛИ-НЕ на транзисторном уровне (а) и его УГО (б)

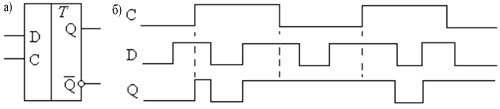

Схемотехника КМОП-триггеров БИС Большой класс элементов памяти (ЭП) в БИС образуют триггеры - это схемы, имеющие два устойчивых состояния, которые устанавливаются при подаче соответствующей комбинации сигналов на управляющие входы и сохраняются в течение заданного времени после окончания действия этих сигналов. Базовым элементом является D-триггер и его разновидности, остальные виды триггеров, например JK, строятся на основе традиционных методов объединения логических вентилей. Для построения вентилей в КМОП-схемах в основном используются три вида схемотехники: статическая, cинхронизируемая динамическая и проходная. В зависимости от типов компонент запоминания, используемых в триггерах, они разделяются на статические, динамические и совмещ╦нные - статико-динамические. Если состояние триггера изменяется по поступлению синхронизирующего сигнала, то такой триггер относят к синхронным. В асинхронных триггерах переключение происходит по поступлению на управляющие входы соответствующей комбинации входных сигналов. В БИС наибольшее распространение получили синхронные триггеры. В статических ЭП занес╦нная информация может сохраняться сколь угодно долго. Основой статического ЭП является бистабильная ячейка, образованная перекр╦стным объединением инвертирующих логических элементов. Динамические ЭП содержат один логический элемент и дополнительный компонент запоминания на принципе накопления заряда со схемами записи. Триггеры, синхронизируемые уровнем синхросигнала, могут изменять сво╦ состояние в течение действия синхронизирующего импульса C при поступлении информационных сигналов на вход D. В течение паузы при изменении уровня синхронизирующего сигнала C их состояние не зависит от уровней входных сигналов. Обозначение триггера показано на рис. 7а, а его временная диаграмма работы показана на рис. 7б. Такие триггеры в зарубежной литературе называют "защ╦лка" (latch), в отечественной - однотактный D-триггер. Буква "Т" на УГО говорит, что это однотактный D-триггер. Рисунок 7. Обозначение (а) и временные диаграммы работы (б) D-триггера, тактируемого уровнем сигнала

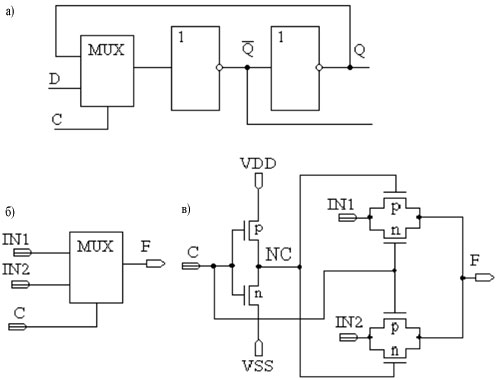

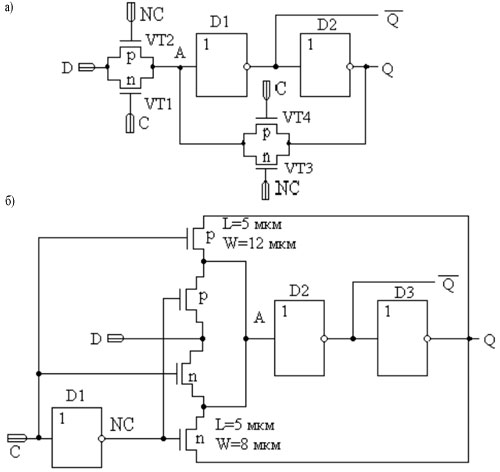

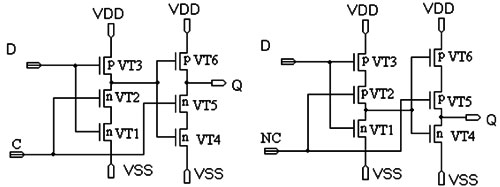

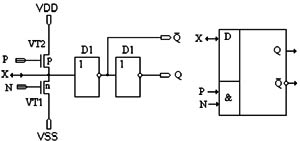

D-триггер, синхронизируемый по уровню в КМОП-схемах, строится на основе мультиплексора (MUX) и бистабильных ячеек логических элементов (рис. 8а). Мультиплексор представляет собой связку проходных ключей, построенных параллельным соединением p- и n-канальных МОП-транзисторов (рис. 8б,в). Рисунок 8. Одноступенчатый D-триггер, синхронизируемый уровнем: а) вентильная реализация одноступенчатого D-триггера; б) обозначение мультиплексора на логическом уровне; в) мультиплексор на проходных ключах

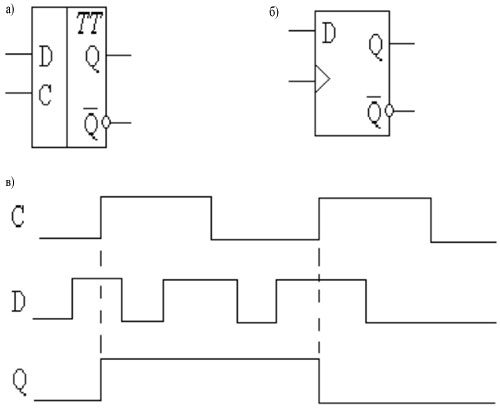

Триггеры, синхронизируемые фронтом сигнала, изменяют сво╦ состояние при поступлении на синхровход соответствующего фронта синхросигнала с положительного либо отрицательного (рис. 9а). При статических уровнях синхросигнала состояние триггера сохраняется, независимо от уровней входных сигналов. Временная диаграмма работы такого триггера показана на рис. 9в. Такие триггеры в отечественной литературе называют двухтактными. Об этом говорят две буквы "ТТ" на УГО. Обозначение двухтактного триггера, принятое в зарубежной литературе, показано на рис. 9б. Треугольник на УГО показывает, что триггер тактируется передним фронтом синхроимпульса. Рисунок 9. Обозначение D-триггера тактируемого фронтом синхросигнала, принятое в отечественной (а) и в зарубежной литературе (б), временные диаграммы работы (в)

В КМОП БИС используют ЭП как на основе простейших бистабильных ячеек, так и на основе более сложных триггеров D-типа. Основным типом ЭП является синхронный D-триггер, тактируемый уровнем синхросигнала. Построение ЭП на основе логических элементов типа И-НЕ в КМОП БИС малоэффективно из-за большого числа компонентов и большой площади, занимаемой на кристалле. Поэтому для использования в БИС высокой сложности берутся усовершенствованные варианты электрических схем D-триггеров, тактируемых уровнем сигнала. D-триггеры на основе проходных ключей Схема D-триггера, тактируемого уровнем на основе двух коммутируемых проходных ключей (первый, входной на транзисторах VT1, VT2; второй, обратной связи на транзисторах VT3, VT4), показана на рис. 10а. Транзисторы VT1√VT4 образуют мультиплексор, инверторы D1 и D2 - бистабильную ячейку. Для тактирования используется двухфазная синхронизация C, NC. Допустим, что на вход C подан высокий уровень сигнала, на вход NC - низкий. Тогда вход ной ключ открыт и переда╦т сигнал со входа D через инвертор D1 на выход Q в инверсной форме, далее через инвертор D2 поступает на выход Q в прямой форме. Рисунок 10. D-триггер, тактируемый уровнем на основе двух коммутируемых проходных ключей: а) двухфазное тактирование; б) однофазное тактирование

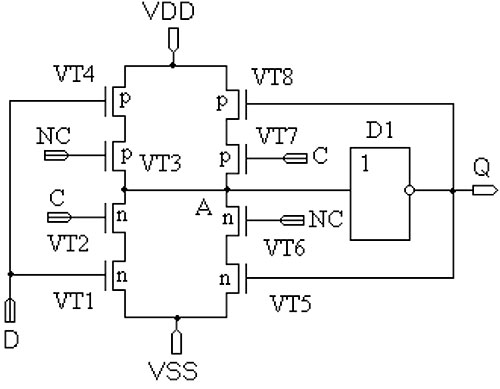

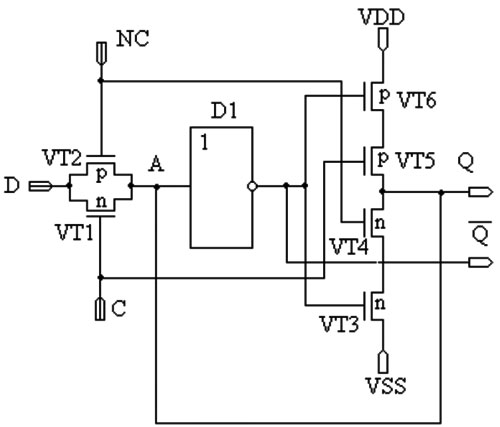

При этом ключ обратной связи закрыт и отключает инвертор D2 от узла A и тем самым разрывает обратную связь в бистабильной ячейке D1 и D2. D-триггер находится в режиме передачи сигнала. При изменении фазы синхросигналов C, NC, на противоположную входной ключ закрывается и изолирует узел A от входа D. При этом на паразитной ╦мкости узла A сохраняется последнее значение уровня сигнала входа D. Одновременно открывается ключ обратной связи, и инверторы D1 и D2 образуют бистабильную статическую ячейку, в которой запоминается уровень сигнала узла A. Триггер переходит в режим хранения сигнала. Возможно упрощение схемы D-триггера пут╦м исключения ключа обратной связи. На рис. 10б представлен D-триггер, тактируемый уровнем на проходных ключах (вариант). По принципу работы схема аналогична схеме на рис. 10а. Схема представлена в виде, удобном для топологической реализации на кристалле. Геометрические размеры всех p-МОП транзисторов берутся равными: длина канала (L) - 5 мкм; ширина канала (W) - 12 мкм. Для n-МОП транзисторов: L = 5 мкм; W = 8 мкм. D-триггеры на основе динамических ключей Схема D-триггера на основе двух динамических ключей-инверторов (первый, входной на транзисторах VT1-VT4, второй, обратной связи, на транзисторах VT5-VT8), с использованием двухфазной синхронизации C, NC, показана на рис.11. Рисунок 11. D-триггер на основе динамических ключей (базовый вариант)

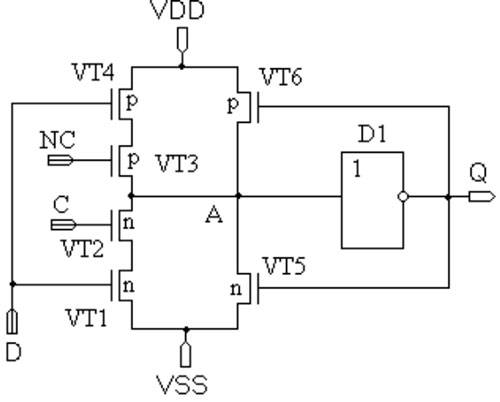

Допустим, на вход С подан высокий уровень сигнала, на вход NC - низкий уровень. При этом транзисторы VT2, VT3 открыты, первый ключ функционирует как обычный инвертор, и входной сигнал со входа D переда╦тся через узел A и логический элемент D1 на выход Q в прямой форме. В этом режиме транзисторы VT6, VT7 закрыты и изолируют транзисторы VT5, VT8 ключа обратной связи от узла A. При изменении фазы синхросигналов (С - на низкий, NC - на высокий) транзисторы VT2, VT3 закрываются и отключают входной ключ от входа D, а в узле А на паразитной ╦мкости сохраняется последний уровень сигнала. При этом транзисторы VT6, VT7 включаются, и ключ обратной связи вместе с логическим элементом D1 образует бистабильную статическую ячейку, в которой запоминается уровень сигнала в узле А, и D-триггер переходит в режим хранения. С целью сокращения компонентов в схеме в качестве инвертора обратной связи возможно применение статического инвертора (транзисторы VT5, VT6, рис. 12). Рисунок 12. D-триггер на основе динамических ключей (с использованием одного статического инвертора)

Однако в такой схеме для переключения из состояния низкого уровня в состояние высокого уровня (на выходе D-триггера) необходимо, чтобы транзисторы VT1, VT2 были способны переключить ток, отдаваемый включенным транзистором VT6, и наоборот, для этого транзисторы VT1-VT4 имеют размеры больше, чем у VT5, VT6. На рис. 13 показаны динамические триггеры с однофазной синхронизацией и с синхронизирующими транзисторами одного типа проводимости. Первая построена на основе двух последовательно соедин╦нных динамических инверторов n-типа. При высоком уровне синхросигнала на входе C синхронизирующие транзисторы VT2, VT5 инверторов открыты, и информационный сигнал с входа D переда╦тся в прямой форме на выход Q. При изменении фазы синхросигнала на противоположную синхронизирующие транзисторы VT2, VT5 закрыты, и в триггере сохраняется уровень последнего передаваемого сигнала. Говорят, что схема такого D-триггера прозрачна для выходного сигнала D по высокому уровню синхросигнала. Вторая схема построена на основе динамических инверторов p-типа и функционирует аналогично первой и прозрачна для выходного сигнала D по низкому уровню синхросигнала. Рисунок 13. Схемы динамических D-триггеров с одним синхровходом: а) прозрачная для логической единицы; б) прозрачная для логического нуля

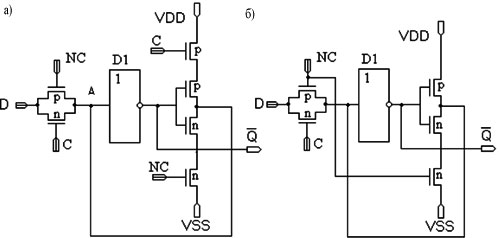

D-триггеры на основе ключей комбинированного типа Схема D-триггера, тактируемого уровнем на основе ключей комбинированного типа, представлена на рис. 14. На входе D схема содержит проходной ключ на транзисторах VT1, VT2, а в цепи обратной связи - динамический ключ на транзисторах VT3, VT6. Допустим, на вход C подан сигнал высокого уровня, а на вход NC - сигнал низкого. Тогда входной ключ открыт, и сигнал с входа D в инверсной форме через инвертор D1 переда╦тся на выход Q в инверсной форме. При этом транзисторы VT4, VT5 выключены и изолируют транзисторы VT3, VT6 ключа обратной связи от узла A. При изменении фазы синхросигналов C, NC, на противоположную входной ключ закрывается и изолирует узел A от входа D. При этом на паразитной ╦мкости узла А сохраняется последний уровень сигнала входа D. Рисунок 14. D-триггер, тактируемый уровнем на основе комбинации ключей двух типов

Одновременно открываются транзисторы VT4, VT5, и включенный ключ обратной связи вместе с инвертором D1 образуют бистабильную ячейку памяти. D-триггер переходит в режим хранения. Иногда используют иное расположение ключевых транзисторов (рис. 15а). С целью упрощения схемы в ключе обратной связи исключают один из синхронизирующих транзисторов (рис. 15б). Рисунок 15. D-триггер комбинированного типа (вариант)

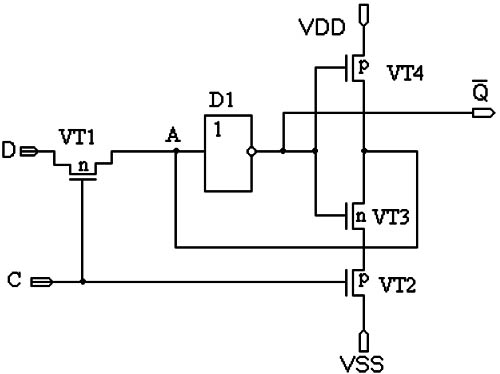

Упростить синхронизацию блоков БИС позволяют D-триггеры, использующие один синхровход C (NC). Схема такого типа, синхронизируемая прямым сигналом, показана на рис. 16. Рисунок 16. D-триггер комбинированного типа с одним прямым синхросигналом

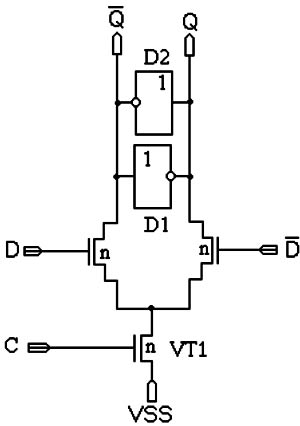

При подаче высокого уровня синхросигнала C транзистор VT1 открыт и обеспечивает передачу сигнала со входа D на выход Q через инвертор D1. Транзистор VT2 при этом закрыт и отключает транзистор обратной связи VT3. Транзистор VT4 способствует регенеративному включению элемента D1 и повышает уровень напряжения в узле A до уровня VDD, пониженный входным транзистором VT1. D-триггеры с дифференциальным входным каскадом Электрическая схема D-триггера с дифференциальным входным каскадом получила распространение в системах "конвейерного" типа как обеспечивающая максимальное быстродействие. Схема содержит бистабильную ячейку на инверторах D1, D2 и синхронизируемый дифференциальный входной каскад на транзисторах VT1-VT3 (рис. 17). При высоком уровне сигнала на синхровходе C синхронизирующий транзистор VT1 открыт, и сигналы со входов D и D передаются на выходы Q и Q. Параллельно с передачей осуществляется запись сигнала в бистабильную ячейку D1, D2. Для устойчивой работы ЭП размеры транзисторов инверторов D1, D2 должны быть меньше размеров транзисторов VT1√VT3. При подаче низкого уровня сигнала на вход C транзистор VT1 закрывает входные транзисторы VT2, VT3 и блокирует передачу сигналов со входов D, D. Триггер переходит в режим хранения, и на выходы Q, Q поступают уровни сигналов, записанные в бистабильной ячейке D1, D2. Рисунок 17. D-триггер с дифференциальным входным каскадом

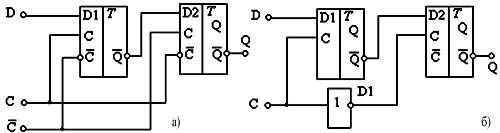

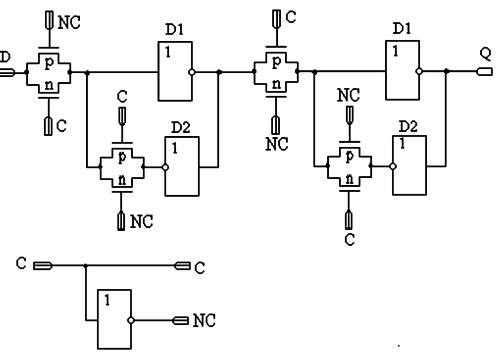

Элементы памяти, тактируемые фронтом синхросигнала В микропроцессорных БИС наиболее употребляемой структурой ЭП, тактируемых фронтом, является структура типа MS (master/slave - ведущий/ведомый). В дальнейшем эти триггеры будем называть двухтактными. Эта структура предполагает последовательное соединение двух D-триггеров, тактируемых уровнем. При этом фаза тактирования первого триггера (ведущего M) противоположна фазе тактирования второго (ведомого S). На рис. 18 приведены базовые схемы D-триггеров, тактируемых фронтом. На рис. 19 показана вентильная реализация статического триггера, синхронизируемого фронтом. Рисунок 18. Базовые схемы D-триггеров, тактируемых фронтом типа MS: а) с двухфазной синхронизацией С, NC; б) с однофазной синхронизацией

Рисунок 19. Схема статического триггера, тактируемого фронтом с однофазной синхронизацией

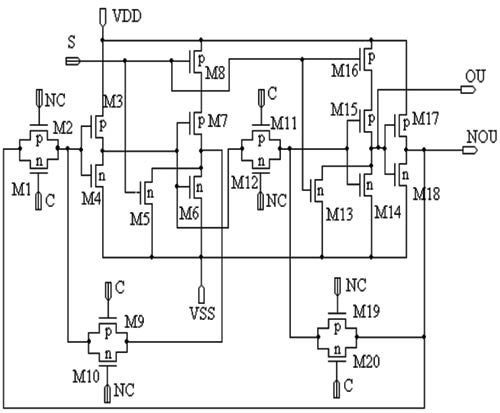

На рис. 20 приведена электрическая схема двухтактного D-триггера (разряд сч╦тчика без занесения данных), используемого, например, в двоичных четырех-разрядных сч╦тчиках. Для данного триггера предусмотрен вспомогательный вход Set, предназначенный для прямой установки триггера. Рисунок 20. Электрическая схема статического двухтактного D-триггера с асинхронным входом установки Set

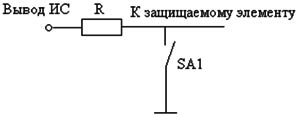

Схемотехника входных ячеек КМОП БИС Базовый принцип защиты ИС от воздействия электростатического разряда (ЭСР) показан на рис. 21. При ЭСР срабатывает двуполярный ключ SA1, и ток разряда отводится на шину питания или земли. Кроме того, часть заряда рассеивается на резисторе R. Идеальная защита достигается, если сопротивление ключа во включенном состоянии и время его включения равны нулю. В ИС в качестве таких шунтов применяются различные элементы: диоды, транзисторы или более сложные схемы. Рисунок 21. Базовый принцип защиты ИС от воздействия ЭСР

Важное требование к защитным структурам - не ухудшать параметры защищаемой ИС. Кроме того, они должны иметь небольшую площадь; эффективно ограничивать напряжение разряда, подаваемого на схему; шунтировать напряжение и токи перегрузки, возникающие при ЭСР; иметь максимально быстрое время срабатывания и вносить минимальное время задержки в нормальную работу ИС. В микросхемах с МОП-транзисторами для защиты от пробоя подзатворного диэлектрика входных транзисторов в простейшем случае используются защитные диоды (рис. 22). Для улучшения защитного действия таких схем применяют дополнительные МОП-транзисторы, резисторы и диоды. Рисунок 22. Защитные диоды входных буферов на КМОП-транзисторах

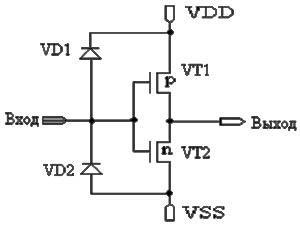

Схемотехника буферных ячеек КМОП БИС Буферные ячейки КМОП БИС предназначены для организации электрического и временного взаимодействия ядра БИС с внешней средой. При соблюдении соответствующих правил соединения внутренних и буферных ячеек обеспечивают соответствующие уровни выходных логических сигналов, нагрузочные способности, времена задержек выходных сигналов и длительности их фронтов и так далее. Часто буферные элементы организуются как двунаправленные с целью формирования двунаправленных входов/выходов БИС. Схемотехника типичного двунаправленного буферного элемента представлена на рис. 23. За сч╦т специальных средств управления входами N и P схемы представляется возможным независимо от ядра логической схемы устанавливать на внешних выводах произвольные логические состояния 0, 1 и H. Рисунок 23. Построение двунаправленной периферийной ячейки (а) и е╦ обозначение на логическом уровне (б)

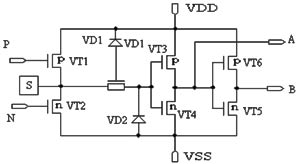

Для буферных элементов площадь p-канального транзистора VT2 больше площади n-канального транзистора VT1, так как Wp ~ 3Wn при Ln ~ Lp. Стоки транзисторов через элементы D1 и D2 соединены с контактной площадкой. На практике входные и выходные периферийные ячейки объединяют в магистральную ячейку. Электрическая схема магистральной ячейки показана на рис. 24. В ячейке имеются мощные транзисторы VT1 и VT2 для поддержки функции "выход", а также диодно-резисторная сборка (VD1, VD2, R), обеспечивающая электростатическую защиту при работе с магистралью (функция "вход"). Таким образом, магистральная ячейка выполняет функцию "вход/выход". S - контактная площадка. Рисунок 24. Электрическая схема магистральной ячейки

В диодно-резисторной сборке (VD1, VD2, R) диод VD2 является самостоятельным элементом конструкции, а диод VD1 составляет единое целое с резистором R. Мощные транзисторы VT1 и VT2, реализующие функцию "выход" при работе на магистраль, формируются пут╦м параллельного включения p-МОП (VT1) и n-МОП (VT2) транзисторов, что обеспечивает набор эффективной ширины каналов. Четыре параллельно включенные p-МОП транзистора дают ширину около 400 мкм, в то время как типичная ширина канала ядра ячейки может составлять величину 7 мкм. Литература

|

Схемотехника элементов БИС.

Схемотехника элементов БИС.